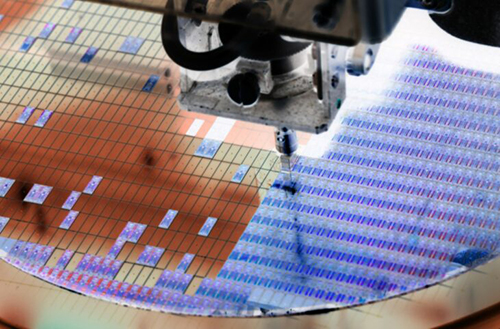

近日,三星与IBM联合与2021年12月国际电子元件会议(International Electron Devices Meeting;IEDM),宣布研发出突破1纳米工艺以下的新晶体管技术。IEDM是一种在芯片上垂直堆叠晶体管的新设计。

目前的处理器和单片机,是将晶体管平放在硅表面上,然后电流从一侧流向另一侧。然而,三星与IBM则宣称研发出垂直传输场效应晶体管(Vertical Transport Field Effect Transistors;VTFET),是透过彼此垂直堆叠之下,让电流垂直流动来达成。

VTFET设计有两个优点。首先,可以绕过许多性能限制,将摩尔定律扩展到1纳米瓶颈之外物理限制。更重要的是,由于电流更大,该设计减少了能源浪费。根据这两家公司的估计,VTFET将使处理器的速度比采用FinFET晶体管设计的芯片快了两倍,且功耗降低85%。

也就是说,采用这种晶体管设计的芯片可能有朝一日允许手机一次充电之下,可以使用整整一周的时间。此外,它还可以使某些需要能源密集型任务(包括:加密采矿)变得更加节能,对与环境的影响也变得较小。由于这是实验室做出来的结果,因此IBM和三星都尚未透露他们计划何时将该设计商业化。

台积电方面,2021年5月中旬,台积电联手台大与MIT才研发出单层(Monolayers)或二维(two-dimensional)材料结合半金属铋(Bi)能达到极低的电阻,接近量子极限,有助与实现半导体1纳米以下的艰巨挑战。

英特尔方面,2021年7月表示,其目标是在2024年之前完成埃级(Angstrom-scale)芯片的设计,也就是1纳米芯片设计。英特尔计划使用其新的英特尔20A节点和RibbonFET晶体管来完成这一设计。

根据Insights预计2027年全球半导体制造设备市场销售额可超越900亿美元。其中,二维技术在2020年占据了超过30%的营收比例,原因是该架构提供了多种功能,例如坚固的结构、低功耗和低成本营运。其也认为合作开发基与二维材料的IC是值得关注的领域。因为在1纳米芯片中使用二维材料可以显着降低半导体中的电阻并增强电流,且较有机会在较早阶段进入实际量产,这是其优势。这也是IBM与三星无法透露采用VTFET技术的1纳米工艺何时可以进入量产的原因。毕竟,研发是一回事,能否进入量产又是另一回事。

以上就是英锐恩单片机开发工程师分享的“三星与IBM宣布突破1纳米工艺晶体管技术”。英锐恩专注单片机应用方案设计与开发,提供8位单片机、16位单片机、32位单片机。